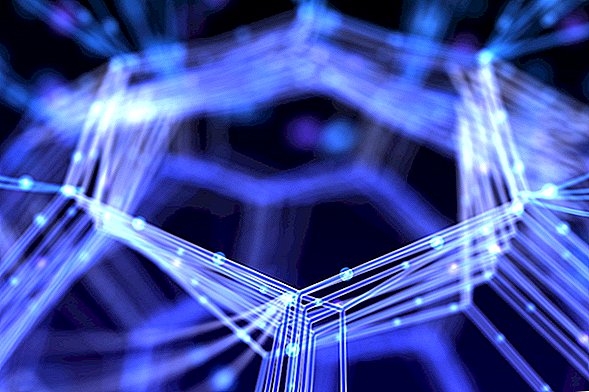

En ny typ av 3D-datorchip som kombinerar två banbrytande nanoteknologier kan dramatiskt öka processorns hastighet och energieffektivitet, säger en ny studie.

Dagens chips separerar minne (som lagrar data) och logiska kretsar (som bearbetar data), och data skickas fram och tillbaka mellan dessa två komponenter för att utföra operationer. Men på grund av det begränsade antalet anslutningar mellan minne och logiska kretsar, blir detta en viktig flaskhals, särskilt eftersom datorer förväntas ta itu med allt större datamängder.

Tidigare maskerades denna begränsning av effekterna av Moores lag, som säger att antalet transistorer som kan passa på ett chip fördubblas vartannat år, med en åtföljande ökning av prestanda. Men när chiptillverkare träffar grundläggande fysiska gränser för hur små transistorer kan få, har denna trend minskat.

Det nya prototypchipet, designat av ingenjörer från Stanford University och Massachusetts Institute of Technology, hanterar båda problemen samtidigt genom att lagra minne och logikkretsar ovanpå varandra, snarare än sida vid sida.

Detta gör inte bara effektiv användning av rymden, utan det ökar också ytan för anslutningar mellan komponenterna dramatiskt, säger forskarna. En konventionell logisk krets skulle ha ett begränsat antal stift i varje kant genom vilken data kan överföras; däremot var forskarna inte begränsade till att använda kanter och kunde packa vertikala trådar som sträcker sig från logikskiktet till minneskiktet.

"Med separat minne och datoranvändning är ett chip nästan som två mycket folkrika städer, men det finns väldigt få broar mellan dem," berättade studieledaren Subhasish Mitra, professor i elektroteknik och datavetenskap vid Stanford, till Live Science. "Nu har vi inte bara sammanfört dessa två städer - vi har byggt många fler broar så att trafiken kan gå mycket mer effektivt mellan dem."

Dessutom använde forskarna logiska kretsar konstruerade av kol nanorörstransistorer, tillsammans med en ny teknik som kallas resistivt random access-minne (RRAM), som båda är mycket mer energieffektiva än kiselteknologier. Detta är viktigt eftersom den enorma energin som behövs för att driva datacentra utgör en annan stor utmaning som teknikföretagen står inför.

"För att få nästa 1000-gånger förbättring av datorprestanda när det gäller energieffektivitet, vilket gör att saker körs med mycket låg energi och samtidigt får saker att köra riktigt snabbt, det här är den arkitektur du behöver," sa Mitra.

Medan båda dessa nya nanoteknologier har inneboende fördelar jämfört med konventionell, kiselbaserad teknik, är de också integrerade i det nya chipets 3D-arkitektur, säger forskarna.

Anledningen till att dagens chips är 2D är att tillverka kiseltransistorer på ett chip kräver temperaturer på mer än 1 800 grader Fahrenheit (1 000 grader Celsius), vilket gör det omöjligt att lägga kiselkretsar ovanpå varandra utan att skada bottenlagret, säger forskarna .

Men både kolananorörstransistorer och RRAM är tillverkade vid kylare än 200 ° C, så att de lätt kan läggas på toppen av kisel utan att skada de underliggande kretsarna. Detta gör också forskarnas tillvägagångssätt kompatibelt med den aktuella chiptillverkningstekniken, sade de.

Att stapla många lager ovanpå varandra kan potentiellt leda till överhettning, sade Mitra, eftersom topplagren kommer att vara långt ifrån kylflänsen vid basen av chipet. Men, tillade han, att problemet bör vara relativt enkelt att konstruera, och den ökade energieffektiviteten i den nya tekniken innebär att mindre värme genereras i första hand.

För att visa fördelarna med dess design byggde teamet en prototyp gasdetektor genom att lägga till ytterligare ett lager kolbaserade nanorörsbaserade sensorer på toppen av chipet. Den vertikala integrationen innebar att var och en av dessa sensorer var direkt anslutna till en RRAM-cell, vilket dramatiskt ökade hastigheten med vilken data kunde bearbetas.

Dessa data överfördes sedan till det logiska lagret, som implementerade en maskininlärningsalgoritm som gjorde det möjligt att skilja mellan ångorna av citronsaft, vodka och öl.

Men detta var bara en demonstration, sa Mitra, och chipet är mycket mångsidigt och särskilt väl lämpat för den typ av datatunga, djupa neurala nätverksstrategier som understödjer den nuvarande tekniken för artificiell intelligens.

Jan Rabaey, professor i elektroteknik och datavetenskap vid University of California i Berkeley, som inte var inblandad i forskningen, sa att han håller med.

"Dessa strukturer kan vara särskilt lämpade för alternativa inlärningsbaserade beräkningsparadigmer som hjärninspirerade system och djupa nervnät, och det sätt som författarna presenterar är definitivt ett bra första steg i den riktningen," sa han till MIT News.